## Universidade Federal do Ceará Departamento de Computação Mestrado e Doutorado em Ciência da Computação

## Fusion: Abstrações Linguísticas sobre Java para Programação Paralela Heterogênea com GPGPUs.

Anderson Boettge Pinheiro

Fortaleza – Ceará Maio de 2013

# Universidade Federal do Ceará Centro de Ciências Departamento de Computação Mestrado e Doutorado em Ciência da Computação

## Fusion: Abstrações Linguísticas sobre Java para Programação Paralela Heterogênea com GPGPUs

## ${\bf Autor}$ Anderson Boettge Pinheiro

#### Orientador

Prof. Dr. Francisco Heron de Carvalho Junior

Dissertação de mestrado apresentada ao Programa de Pós-graduação em Ciência da Computação da Universidade Federal do Ceará como parte dos requisitos para obtenção do título de Mestre em Ciência da Computação.

Fortaleza – Ceará Maio de 2013

#### Dados Internacionais de Catalogação na Publicação Universidade Federal do Ceará Biblioteca de Ciências e Tecnologia

#### P718f Pinheiro, Anderson Boethge.

Abstrações linguísticas sobre Java para programação paralela heterogênea sobre GPGPUs. / Anderson Boethge. -2013.

140f.: il., color., enc.; 30 cm.

Dissertação (mestrado) – Universidade Federal do Ceará, Centro de Ciências, Departamento de Computação, Programa de Pós Graduação em Ciência da Computação, Fortaleza, 2013.

Área de Concentração: Engenharia de Software.

Orientação: Prof. Dr. Francisco Heron de Carvalho Junior.

1. Programação paralela (Computação). 2. Java (Linguagem de programa de computador). 3. Arquitetura de computador. I. Título.

CDD 005

## Agradecimentos

Esta dissertação é fruto de muito trabalho e dedicação e não poderia deixar de deixar aqui meus agradecimentos a todos que estiveram ao meu lado durante esse período, apoiando e compreendendo aqueles momentos em que não estive presente

Ao meu professor e orientador Heron, pela dedicação e permanente apoio. Aos seus ensinamentos, sua forma amiga, exigente e crítica, de fundamental contribuição no meu crescimento enquanto pesquisador.

Aos meus pais Gilnei e Vera, que souberam apoiar uma decisão tão difícil quanto a de um filho sair de casa para buscar seu caminho. A distância tornou tudo mais difícil mas hoje estamos colhendo os frutos daquilo que plantamos a dois anos atrás, e isso graças a vocês que sempre compreenderam minhas decisões, muito obrigado.

A minha namorada, amiga e companheira Francinize, pelo carinho, paciência e compreensão. A gradeço muito por seu incansável apoio, em todos os momentos durante o desenvolvimento desse trabalho.

A toda minha família, por não apenas apoiar a mim mas também aos meus pais que durante esse período tenho certeza tiveram todo apoio de todos vocês, inclusive naqueles momentos mais difíceis em que não pude estar ai com vocês, agradeço profundamente a todos.

Por fim, deixo aqui minha sincera gratidão a todas as pessoas que, direta ou indiretamente, contribuíram para a concretização deste trabalho.

"O saber a gente aprende com os mestres e os livros.

A sabedoria, aprende-se é com a vida e com os humildes."

Cora Coralina

"Ando impressionado com a urgência do fazer.

Saber não  $\acute{e}$  o suficiente: precisamos aplicar.

Estar disposto não é o suficiente: precisamos fazer."

Leonardo da Vinci

#### Resumo

Unidades de aceleração gráfica, ou GPU (Graphical Processing Units), tem se consolidado nos últimos anos para computação de propósito geral, para aceleração de trechos críticos de programas que apresentam requisitos severos de desempenho quanto ao tempo de execução. GPUs constituem um dentre vários tipos de aceleradores computacionais de propósito geral que tem sido incorporados em várias plataformas de computação de alto desempenho, com destaque também para as MIC (Many Integrated Cores) e FPGA (Field Programmable Gateway Arrays). A despeito da ênfase nas pesquisas de novos algoritmos paralelos capazes de explorar o paralelismo massivo oferecido por dispositivos GPGPU, ainda são incipientes as iniciativas sobre novas abstrações de programação que tornem mais simples a descrição desses algoritmos sobre GPGPUs, sem detrimento à eficiência. Ainda é necessário que o programador possua conhecimento específico sobre as peculiaridades da arquitetura desses dispositivos, assim como técnicas de programação que não são do domínio mesmo de programadores paralelos experientes na atualidade. Nos últimos anos, a NVIDIA, indústria que tem dominado a evolução arquitetural dos dispositivos GPGPU, lançou a arquitetura Kepler, incluindo o suporte às extensões Hyper-Q e Dynamic Parallelism (DP), as quais oferecem novas oportunidades de expressão de padrões de programação paralela sobre esses dispositivos. Esta dissertação tem por objetivo a proposta de novas abstrações de programação paralela sobre uma linguagem orientada a objetos baseada em Java, a fim de expressar computações paralelas heterogêneas do tipo multicore/manycore, onde o dispositivo GPU é compartilhado por um conjunto de threads paralelas que executam no processador hospedeiro, em um nível de abstração mais elevado comparado às alternativas existentes, porém ainda oferecendo ao programador total controle sobre o uso dos recursos do dispositivo. O projeto das abstrações dessa linguagem proposta, doravante chamada Fusion, parte da expressividade oferecida pela arquitetura Kepler.

### Abstract

Graphics Processing Units (GPUs) have been consolidated in the recent years for general purpose computing, aimed at accelerating critical sections of programs that exhibit high performance requirements. GPUs constitute one among a set of classes of general-purpose computational accelerators, which have been incorporated in many high performance computing platforms. Other important classes are MICs (Many Integrated Cores) and FPGAs (Field Programmable Gateway Arrays). In spite of the many research works on new parallel algorithms for exploiting the massive parallelism offered by GPU devices, the initiatives on new programming abstractions that aims at simplifying the description of these algorithms on GPUs, without detriment to efficiency, are still incipient. The programmer still needs specific knowledge about the peculiarities of the target GPU architecture, as well as programming techniques that are complex even for parallel programmers with large experience. In the recent years, NVIDIA, one of the main GPU providers, launched the Kepler architecture, including the support for the Hyper-Q and Dynamic Parallelism (DP) extensions, which offer new opportunities for increasing the expressiveness of parallel programming interfaces on describing patterns of parallel computation using these devices. This work aims at proposing new parallel programming abstractions in a object-oriented language based on Java, for expressing heterogeneous multicore/manycore parallel computations, where the GPU device is shared by a set of parallel threads that runs in the host processor, at a higher level of abstraction compared to the existing alternatives, but still offering to the programmer total control over the device resource usage. design of the abstractions of the proposed language, so-called Fusion, starts from the expressiveness offered by the Kepler architecture.

## Sumário

| 1        | T 4 | du~                                                  | 1              |

|----------|-----|------------------------------------------------------|----------------|

| 1        |     | rodução                                              | 1<br>3         |

|          | 1.1 | Programação para GPUs                                |                |

|          | 1.2 | Orientação a Objetos em Programação para GPUs        | 4              |

|          | 1.3 | Computação Heterogênea - Multicore/Manycore          | 5              |

|          | 1.4 | Problema de Pesquisa                                 | 6              |

|          | 1.5 | Objetivos                                            | 8              |

|          |     | 1.5.1 Objetivo Geral                                 | 8              |

|          | 4.0 | 1.5.2 Objetivos Específicos                          | 8              |

|          | 1.6 | Metodologia                                          | 8              |

|          | 1.7 | Organização do Documento                             | 10             |

| <b>2</b> | Cor | nputação com Unidades de Processamento Gráfico (GPU) | 12             |

|          | 2.1 | Arquitetura GPU                                      | 13             |

|          |     | 2.1.1 Pipeline Gráfico                               |                |

|          |     | 2.1.2 Pipeline Programável                           |                |

|          | 2.2 | GPGPU ou GPU Computing                               |                |

|          | 2.3 | Evolução                                             | 17             |

|          | 2.4 | Programação                                          | 19             |

|          | 2.5 | CUDA                                                 | 20             |

|          |     | 2.5.1 Arquitetura                                    | 21             |

|          |     | 2.5.2 Modelo de Programação                          | $\frac{1}{21}$ |

|          | 2.6 | Portabilidade                                        |                |

|          |     | 2.6.1 Arquitetura Kepler                             |                |

| 3        | Lin | guagens de Programação para GPGPU                    | 39             |

|          | 3.1 | hiCUDA                                               | 39             |

|          | _   | 3.1.1 O Compilador hiCUDA                            | 41             |

|          |     | 3.1.2 Exemplos de Programa em hiCUDA                 | 43             |

|          | 3.2 | CUDA Fortran                                         | 45             |

|          | 3.3 | JCuda                                                |                |

|          | 5.5 | 3.3.1 O Compilador JCuda                             |                |

|          | 3.4 | pyCUDA                                               |                |

|          | 3.5 | Chestnut                                             |                |

|          | 3.6 | JaBEE                                                |                |

|          | J.U |                                                      |                |

Sumário

|              | 3.7         | Rootbeer                                                | 55       |  |  |  |  |  |

|--------------|-------------|---------------------------------------------------------|----------|--|--|--|--|--|

|              | 3.8         | Avaliação de Desempenho                                 | 59       |  |  |  |  |  |

| 4            | <b>Δ</b> Τ. | inguagem Fusion                                         | 62       |  |  |  |  |  |

| _            | 4.1         | 8 8                                                     |          |  |  |  |  |  |

|              | 1.1         | 4.1.1 Usuários Alvo                                     | 63<br>63 |  |  |  |  |  |

|              |             | 4.1.2 Paradigma de Programação: Orientação a objetos    | 64       |  |  |  |  |  |

|              |             | 4.1.3 Transparência sobre Detalhes Arquiteturais da GPU | 66       |  |  |  |  |  |

|              |             | 4.1.4 Programação Paralela Heterogênea                  | 67       |  |  |  |  |  |

|              | 4.2         | Modelo de Programação de Fusion                         | 68       |  |  |  |  |  |

|              | 7.2         | 4.2.1 Objeto Acelerador                                 | 68       |  |  |  |  |  |

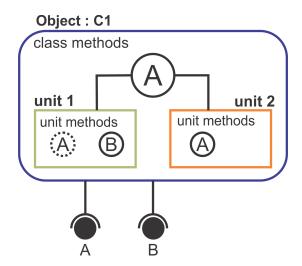

|              |             | 4.2.2 Classe de Objetos Aceleradores                    | 70       |  |  |  |  |  |

|              |             | 4.2.3 Configuração de Grade                             | 74       |  |  |  |  |  |

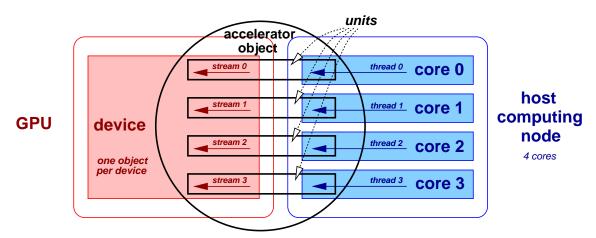

|              |             | 4.2.4 Unidades e Streams                                | 75       |  |  |  |  |  |

|              |             | 4.2.5 Instanciação de Objetos Aceleradores              | 77       |  |  |  |  |  |

|              |             | 4.2.6 Hierarquias de Memória                            | 79       |  |  |  |  |  |

|              |             | 4.2.7 Comunicação                                       | 80       |  |  |  |  |  |

|              |             | 4.2.8 Sincronização                                     | 81       |  |  |  |  |  |

|              |             | 11210 Shiotonibayac                                     | 01       |  |  |  |  |  |

| 5            | _           | elementação e Estudos de Caso                           | 83       |  |  |  |  |  |

|              | 5.1         | Arquitetura do Compilador                               |          |  |  |  |  |  |

|              |             | 5.1.1 Compilador LLVM                                   |          |  |  |  |  |  |

|              |             | 5.1.2 Projeto VMKit                                     |          |  |  |  |  |  |

|              |             | 5.1.3 Versão inicial e funções                          |          |  |  |  |  |  |

|              | 5.2         | Primeiro Estudo de Caso: Multiplicação de Matrizes      | 90       |  |  |  |  |  |

|              | 5.3         | Segundo Estudo de Caso: Enumeração Completa             | 98       |  |  |  |  |  |

|              | 5.4         | Considerações                                           | L03      |  |  |  |  |  |

| 6            | Con         | Conclusões e Trabalhos Futuros 10                       |          |  |  |  |  |  |

|              | 6.1         | Cumprimento dos Objetivos                               | 105      |  |  |  |  |  |

|              |             | 6.1.1 Trabalhos Futuros                                 | 108      |  |  |  |  |  |

| D.           | .fonê       | noing Dibliográfians                                    | 1 5      |  |  |  |  |  |

| Ωŧ           | eierei      | ncias Bibliográficas 1                                  | 15       |  |  |  |  |  |

| $\mathbf{A}$ |             |                                                         | 16       |  |  |  |  |  |

|              | A.1         | Código Java                                             |          |  |  |  |  |  |

|              | A.2         | Código CUDA C                                           |          |  |  |  |  |  |

|              | A.3         | Código Fusion                                           |          |  |  |  |  |  |

|              |             | A.3.1 Classe MatrixMultiUnits                           | 122      |  |  |  |  |  |

|              |             | A.3.2 Classe MatrixAccel                                | 125      |  |  |  |  |  |

| В            | Estı        | ıdo de Caso 2                                           | 27       |  |  |  |  |  |

|              | B.1         | Código CUDA C                                           |          |  |  |  |  |  |

|              |             | Código Fusion                                           |          |  |  |  |  |  |

|              |             | B.2.1 Classe Application                                |          |  |  |  |  |  |

|              |             | B.2.2 Classe TaskEnumaration                            |          |  |  |  |  |  |

| Sumário |       |                         | iii   |

|---------|-------|-------------------------|-------|

|         | B.2.3 | Classe EnumerationAccel | . 138 |

## Capítulo 1

## Introdução

Nos dias atuais, o grau de interesse pela computação paralela tem se tornado cada vez maior, em função da disseminação e consolidação de processadores de múltiplos núcleos em computadores de propósito geral nas mais diversas categorias, incluindo smartphones, tablets, laptops, desktops, servidores e plataformas de computação de alto desempenho (CAD), tais como *clusters* e de processamento paralelo massivo (MPPs - Massive Parallel Processors). Além dos tradicionais nichos de aplicação da computação paralela, notadamente em aplicações científicas e de engenharia com requisitos de CAD, novos nichos de aplicação tem buscado na computação paralela a resolução mais rápida de problemas conhecidos e que exigem algum esforço computacional. Tendo em vista esse contexto, onde a computação paralela assume notável grau de importância, muitas frentes de pesquisa tem se dedicado à busca de novas ferramentas e tecnologias que possam auxiliar no desenvolvimento de software com ênfase no paralelismo. Contudo, para exploração eficiente do paralelismo, são necessários, além de um hardware especializado, modelos de programação que consigam explorar os seus recursos adequadamente, de forma a obter o melhor desempenho em função de características de cada aplicação.

Simultaneamente à consolidação dos processadores de múltiplos núcleos (multicore), os aceleradores computacionais emergiram na área de CAD, como dispositivos associados aos processadores de uma plataforma computacional para realizar tarefas específicas de alto custo computacional em um tempo de processamento viável, impossível de ser atingido por meio de um processador convencional. Os principais tipos de aceleradores computacionais são FPGAs (Field-Programmable Gateway Arrays) [Herbordt et al. 2007], GPUs (Graphical Processing Units) [Pharr e Fernando 2005] e MICs (Many Integrated Cores) [Duran

e Klemm 2012].

FPGAs consistem de unidades de *hardware* com um arranjo de portas lógicas programáveis, permitindo que os usuários programem seu comportamento de acordo com suas necessidades [Herbordt et al. 2007], sendo de natureza intrinsecamente diferentes de GPUs e MICs.

Uma característica comum aos aceleradores computacionais é o uso massivo do paralelismo. No caso de GPUs e MICs, isso envolve envolve o uso de uma grande quantidade de núcleos simplificados de processamento, o que motiva o uso do termo manycore para diferenciá-los da abordagem multicore dos processadores convencionais modernos com os quais cooperam nas plataformas de computação onde são empregados.

Cronologicamente, o surgimento de dispositivos GPU antecede o surgimento de dispositivos MIC, sendo sua disseminação e consolidação fortemente motivada pela sua origem como aceleradores gráficos, no amplo mercado de jogos de computador e aplicações de computação gráfica, antes de se tornarem uma alternativa real no mercado de computação de propósito geral, em especial no restrito, embora crescente, mercado de computação de alto desempenho. Por esse motivo, GPUs são ofertadas no mercado em modelos de custo variado, em geral acessível para equipar os computadores de usuários domésticos e de pequenas corporações.

Enquanto isso, MICs foram propostos recentemente no contexto da concorrência industrial como uma alternativa às GPUs, tendo seu marco no lançamento do processador Intel Xeon Phi e motivados pelo forte interesse das aplicações em aceleradores computacionais. Em relação às GPUs, MICs buscam oferecer um modelo de programação mais adequado à computação de propósito geral, diminuindo certas barreiras ao uso disseminado de GPUs, relacionadas às dificuldades em lidar com seu modelo de programação, que estão intrinsecamente relacionadas as motivações do trabalho de pesquisa dessa dissertação. No entanto, MICs, como é o caso do Intel Xeon Phi, tem sido inicialmente lançados para o restrito mercado de computação de alto desempenho, possuindo custo que se equivale ao de GPUs de topo de linha, também voltadas a esse mercado, tal como a linha Tesla da NVIDIA.

Esse trabalho de pesquisa está particularmente interessado em programação voltada aos dispositivos de aceleração computacional do tipo GPU, tendo em vista a sua maior disseminação e consolidação no mercado ao tempo do início desse projeto, o qual se mantém atualmente.

#### 1.1 Programação para GPUs

As GPUs surgiram no final da década de 1970, como unidades de processamento de propósito especial voltadas à computação gráfica em duas dimensões, com aplicação em jogos de computador e aceleração de programas gráficos de interesse da engenharia. Somente em meados da década de 1990, surgiram os primeiros dispositivos para computação gráfica em três dimensões, porém mantendo sua única finalidade no processamento gráfico. Entretanto, a evolução das GPUs na década de 1990 e início dos anos 2000 permitiu que alguns estágios do chamado pipeline gráfico pudessem ser (re)programados, viabilizando uma maior flexibilidade no uso desses dispositivos que permitiu sua aplicação em computação de propósito geral, dando origem ao termo GPGPU (General-Purpose Graphics Processing Units).

Logo, percebendo o potencial da arquitetura GPU para uma vasta área de aplicações, diversas iniciativas de pesquisa começaram o desenvolvimento das primeiras linguagens de programação capazes de fazer uso dos recursos disponibilizados por esses dispositivos, com destaque para a primeira linguagem desenvolvida no âmbito acadêmico, conhecida como BrookGPU [Buck et al. 2004], desenvolvida por pesquisadores da universidade de Utah nos Estados Unidos.

Entretanto, ainda se faz necessário um modelo de programação para GPUs capaz de expressar de forma mais natural as aplicações, ainda assim permitindo explorar as peculiaridades da arquitetura da GPU alvo. A principal solução para programação sobre GPUs proposta em meados dos anos 2000, com relação a portabilidade de programas, foi a arquitetura CUDA (Computer Unified Device Architecture) da empresa NVIDIA, tornando essa abordagem mais difundida e utilizada até os dias atuais. A arquitetura CUDA tem por premissa expor o dispositivo GPU como um coprocessador aritmético, expondo os seus processadores conhecidos como multiprocessadores de fluxo (SM, do inglês Stream Multiprocessor) para serem utilizados na computação paralela de um determinado conjunto de operações. Entretanto, CUDA ainda é uma linguagem de baixo nível de abstração, exigindo conhecimento especializado por parte do desenvolvedor.

Outras linguagens e ferramentas vem surgindo ao longo dos anos. Em sua grande maioria, incorporam a uma determinada linguagem muito difundida o suporte para ligação à computações descritas na arquitetura CUDA, tais como CUDA Fortran [Fortran 2012] e JCuda [Yan, Grossman e Sarkar 2009], as quais estendem as linguagens Fortran e Java, respectivamente.

Algoritmos e Técnicas de Programação GPGPU Simultaneamente aos esforços nas áreas de linguagens e modelos de programação, devemos ressaltar a grande quantidade de trabalhos de pesquisa, publicados em periódicos científicos de alta reputação, que tem se dedicado a apresentar a implementação de algoritmos conhecidos sobre GPUs, buscando utilizar seus recursos de forma otimizada a fim de minimizar o tempo de execução desses algoritmos a um patamar inalcançável utilizando-se processadores de arquitetura convencional. Embora esse trabalho de pesquisa esteja intrinsecamente relacionado com os esforços na área de linguagens de programação para GPUs, os esforços na área de implementação de algoritmos não são considerados menos importantes, tendo sido utilizados para entender as técnicas de programação comumente usadas sobre essas plataformas.

#### 1.2 Orientação a Objetos em Programação para GPUs

A busca por um nível mais elevado de abstração na programação para dispositivos GPU conduz várias linhas de pesquisas às linguagens orientadas a objetos, cuja importância é atualmente de tal elevado nível para a indústria do software que serve como base para quase todas as técnicas e métodos de sucesso na engenharia de software moderna, o que faz relevante estudar formas de usá-las para programação de computações sobre GPUs.

Linguagens orientadas a objetos tem por premissa a abstração de dados, permitindo a modelagem de um problema real através da abstração de objetos que trocam mensagens através de invocação de seus métodos particulares. Um objeto possui uma propriedade chamada de encapsulamento, na qual abstrai a sua implementação mantendo encapsulados seus atributos e métodos, disponibilizando apenas uma interface para a aplicação ter acesso a suas funções. Ou seja, a aplicação não tem conhecimento sobre a implementação do objeto, mas supõe que ele vai retornar o resultado correto previsto pelos seus métodos. Além disso, o mecanismo de herança, entre classes de objetos que descrevem os atributos e métodos comuns de objetos que representam entidades de mesma natureza, permite a hierarquização de conceitos de forma abstrata e evita a redundância de código.

No entanto, a orientação a objetos é difícil de ser conciliada com arquiteturas GPU, devido as características inerentes a essa arquitetura. Isso justifica o fato de que a maioria dos trabalhos relacionados busquem apenas uma conexão direta com a arquitetura CUDA, pouco preocupada com a proposta de novas abstrações para compatibilizar a orientação a objetos com a programação GPGPU, problema

de interesse nesse trabalho.

#### 1.3 Computação Heterogênea - Multicore/Manycore

Com o advento de GPUs como uma alternativa para acelerar trechos computacionalmente intensivos de programas em aplicações de CAD, as plataformas heterogêneas de computação paralela tornaram-se uma tendência nesse domínio. Por exemplo, o projeto de arquiteturas de cluster computing constituídos de centenas de nós de processamento distribuído, onde cada nó é composto por vários processadores multicore compartilhando um espaço de memória, cada qual associado a um coprocessador manycore, como uma GPU, é uma tendência na lista Top500 [TOP 500 2013], dos 500 mais rápidos computadores paralelos, atualizada semestralmente, já há alguns anos. O mesmo vale para plataformas de arquitetura MPP.

Dentre os computadores listados na lista Top500 de novembro de 2012, 12,4% fazem uso de algum tipo de acelerador computacional, incluindo as GPUs, as quais dominam essa lista respondendo por 10,6% do total (53 máquinas). Porém, em relação ao total de desempenho bruto das máquinas, o impacto das GPUs chega 19,6%, por equiparem máquinas que estão mais ao topo da lista, o que evidencia serem uma tendência na arquitetura de clusters e MPPs. Enquanto isso, já existem 7 máquinas que fazem uso do recém-lançado processador *Intel Xeon Phi*, principal representante da classe MIC.

Em plataformas heterogêneas de computação paralela, o potencial de paralelismo que pode ser explorado pela aplicação encontra-se em vários níveis hierárquicos, que somente podem ser explorados de maneira eficiente com o uso de técnicas e modelos de programação específicos para cada nível, tais como:

- ► MPI [Dongarra et al. 1996] para troca de mensagens entre processos distribuídos no nós de processamento;

- ▶ OpenMP [OpenMP Architecture Review Board 1997] para sincronização entre threads sobre os núcleos de processamento de um nó de processamento;

- ► CUDA, ou OpenCL, para explorar o paralelismo do acelerador computacional, se este for do tipo GPU.

Junte-se a isso a existência de múltiplas hierarquias de memória, que ampliam ainda mais o grau de complexidade da programação eficiente nessas plataformas.

1.4. Problema de Pesquisa 6

Mesmo em computadores desktop ou servidores, vistos individualmente, a computação heterogênea se faz relevante, tendo em vista a proliferação, já amplamente disseminada, da tecnologia de processadores de múltiplos núcleos, que faz do processamento paralelo dentro do processador hospedeiro uma suposição importante que deve ser levada em conta em uma linguagem voltada a conexão entre uma computação nele realizada e a GPU.

Outro fator importante, que tem sido levado em consideração para o uso de GPUs, é a preocupação com o consumo de energia, já que uma característica importante desses dispositivos é o baixo consumo de energia, quando comparadas aos processadores convencionais, alcançando picos de desempenho superiores a um custo energético relativamente menor. As arquiteturas GPU mais recentes possuem preocupação mais enfática em relação aos aspectos de eficiência energética. Um exemplo disso é a arquitetura Kepler [KeplerGK110 2012], da empresa NVIDIA.

Enfim, a computação heterogênea diminui os custos, financeiros e energéticos, para o desenvolvimento de aplicações que exijam um alto poder computacional e que possuam paralelismo massivo, em um contexto onde há limitações na quantidade de núcleos de processamento que podemos incorporar a um processador multicore, tanto em relação a gargalos arquiteturais quanto ao custo energético. Mesmo aplicações que não se enquadram nessas características ainda assim podem obter desempenho sobre arquiteturas GPU, desde que bem implementadas [Pilla e Navaux 2010].

Tendo em vista o contexto apresentado nesta seção, esse trabalho de pesquisa está interessado em oferecer contribuições no contexto da computação heterogênea, notadamente na ligação entre processadores multicore e coprocessadores manycore do tipo GPU, que é de interesse não apenas de aplicações tradicionais de CAD, mas também de quaisquer aplicações que necessitem do uso de GPUs para acelerar sua computação, tendo em vista que quase todos os processadores que equipam os computadores atuais são compostos de múltiplos núcleos.

#### 1.4 Problema de Pesquisa

O avanço, tanto em relação à arquitetura dos dispositivos GPU quanto ao seu modelo de programação, é evidente. No entanto, algo a ser aprimorado é a possibilidade de obter-se um alto nível de abstração na programação sem prejudicar o desempenho das aplicações frente a todo o poder computacional oferecido pelos aceleradores gráficos. No contexto da computação paralela heterogênea, esse problema se torna ainda mais desafiador, tendo em vista a necessidade de conciliar

1.4. Problema de Pesquisa 7

de forma coerente modelos de programação totalmente distintos.

Neste trabalho em particular, nos restringimos ao caso da ligação entre processadores multicore e coprocessadores manycore do tipo GPU. Além disso, desejamos usufruir do potencial de linguagens de programação orientadas a objetos, devido a sua capacidade de abstração, compatibilidade das modernas técnicas de engenharia de software, e maior difusão na comunidade.

Com isso, a principal questão a ser respondida por esse trabalho é:

Novas abstrações linguísticas podem ser incorporadas a uma linguagem de programação orientada a objetos já difundida a fim de facilitar o uso de um dispositivo GPU, sem gargalos de sincronização, por um programa paralelo que executa sobre um processador multicore?

Mesmo com a existência de linguagens de alto poder de abstração, essa ainda é uma questão que gera discussões. Apesar de tornar mais simples a descrição de operações complexas sobre a GPU, conciliar abstrações de alto nível e desempenho não é algo trivial. Em uma interface de programação de alto nível, não são todas as aplicação que conseguem explorar o desempenho potencial da arquitetura GPU. Em geral, são voltadas a facilitar o desenvolvimento de uma certa classe de aplicações, com características específicas.

Ainda que novos projetos desenvolvam ferramentas para facilitar e reduzir a complexidade da programação sobre GPUs, não existe um padrão que garanta a melhor utilização dos recursos, de modo que o programador necessita ter um conhecimento aprofundado sobre os detalhes da arquitetura alvo, bem como sobre as características da aplicação, para obter o melhor desempenho.

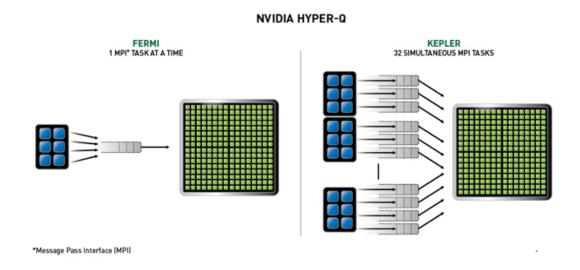

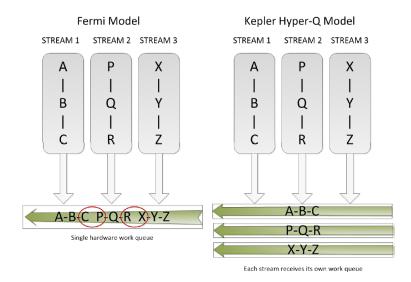

Portanto, a principal limitação na utilização de GPUs para propósito geral é a intima relação entre desempenho e as características da arquitetura alvo, impedindo que os modelos computacionais atuais consigam obter o desempenho máximo ofertado por dispositivos GPUs, de especial interesse na área de CAD. Contudo, os avanços tecnológicos tem permitido um nível mais elevado de expressividade dos modelos, removendo limitações que antes impediam alguns padrões de programação paralela serem aplicados nas aplicações de propósito geral. As principais inovações são as tecnologias Hyper-Q e paralelismo dinâmico (DP, do inglês dynamic Paralellism), da recente Kepler GK110. A Hyper-Q permite a execução de até 32 fluxos de operações em paralelo algo de importância para CAD, além de, através da tecnologia DP, permitir o lançamento de novos trabalhos diretamente no dispositivo,

1.5. Objetivos

evitando comunicações entre hospedeiro e dispositivo que podem comprometer o desempenho das aplicações.

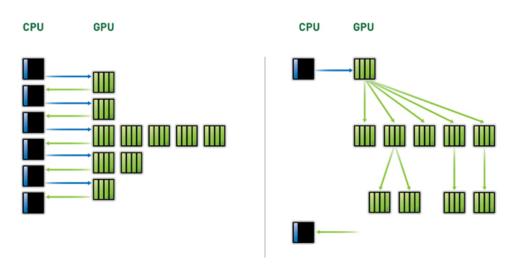

O paralelismo a nível de threads, amplamente difundido pela programação paralela em sistemas de computação paralela multicore, nos remete a utilização da tecnologia Hyper-Q para conexão de diferentes threads de uma aplicação multithread com um ou mais dispositivos GPU. De fato, essa e outras extensões tecnológicas são de especial interesse aos objetivos deste trabalho, por tornarem possível a implementação das abstrações propostas como resultado desse trabalho, a fim de responder a sua questão de pesquisa.

#### 1.5 Objetivos

#### 1.5.1 Objetivo Geral

O objetivo geral desse trabalho é o desenvolvimento de abstrações linguísticas sobre uma linguagem de programação orientada a objetos, com o propósito de encapsular a complexidade da ligação com dispositivos GPUs de programas paralelos multicore, em um contexto de computação heterogênea envolvendo processadores multicores e coprocessadores manycore.

#### 1.5.2 Objetivos Específicos

Para alcançar o objetivo geral, identificamos os seguintes objetos específicos para esse trabalho:

- i. Caracterizar as principais técnicas de programação utilizadas por programadores das áreas de ciências e engenharias, os principais usuários de plataformas heterogêneas de computação paralela, sobre GPUs;

- ii. Identificar e classificar as principais limitações das abordagens sobre linguagens orientadas a objetos de programação para dispositivos GPUs;

- iii. Caracterizar o potencial de expressividade para descrição de padrões de computação paralela de novas tecnologias suportadas por novas arquiteturas de dispositivos, tais como Hyper/Q e Paralelismo Dinâmico.

#### 1.6 Metodologia

A proposta de novas linguagens de programação, suportando novas abstrações algumas das quais também poderiam ser incorporadas em linguagens já existentes, exige um conhecimento mais aprofundado sobre como os programadores tem feito

1.6. Metodologia

uso dos recursos de programação paralela sobre GPUs para o usufruto das aplicações que desenvolvem. Para tal propósito, é necessário ao pesquisador debruçar-se sobre a vasta literatura que tem sido produzida, desde a segunda metade da década de 2000, a respeito do desenvolvimento de programas usando aceleradores gráficos, especialmente no contexto de aplicações de interesse científico. Por esse motivo, esse trabalho de pesquisa iniciou com um estudo exploratório sobre artigos onde são apresentadas implementações de algoritmos importantes nas áreas de ciências e engenharias, com alta demanda computacional. Para garantir que a abrangência desse estudo seja relevante, foi adotada a taxonomia *Dwarf Mine* [Asanovic et al. 2006], a qual organiza algoritmos de interesse de aplicações científicas de acordo com características relevantes como padrões de comunicação entre processos e de acesso à memória. Entretanto, o resultado desse estudo exploratório não é apresentado nessa dissertação, apesar da sua relevância para construção dos seus resultados.

Iniciou-se então uma busca por ferramentas e linguagens de programação para GPGPU, visando analisar suas principais características e limitações com relação a programação sobre plataformas paralelas heterogêneas. Esse estudo permite a identificação das estratégias de mapeamento e construção das estruturas para os dispositivos GPUs, adotadas por cada um dos trabalhos relacionados. Verificou-se, com isso, as dificuldades em aliar um alto nível de abstração com alto desempenho sobre arquiteturas GPGPU.

Após a etapa exploratória sobre o contexto no qual está inserido esse trabalho, obteve-se o conhecimento necessário para iniciar o desenvolvimento desse trabalho. Seguindo o principal objetivo, era necessário escolher uma linguagem de alto nível que pudesse de alguma forma ser estendida com novas abstrações capazes de realizar flexibilizar o desenvolvimento de aplicações sobre duas arquiteturas distintas, encontradas nas plataformas paralelas heterogêneas. A linguagem escolhida foi a linguagem Java, devido ao seu caráter orientado a objetos e o fato de ser uma linguagem já consolidada e amplamente difundida.

As abstrações pretendidas tem como principal preocupação explorar ao máximo os benefícios da orientação a objetos. Tendo como base uma aplicação multithread, as abstrações devem estabelecer uma ponte entre a aplicação e um dispositivo GPU na forma de objetos aceleradores. Abstrações baseadas na orientação a objetos podem ser favoráveis aos usuários, permitindo que dediquem mais tempo para a modelagem da aplicação em si, abstraindo-se de conceitos específicos da arquitetura do hardware da GPU alvo.

Com isso, esse trabalho tem como resultado o protótipo de linguagem de programação que estende a linguagem Java, a qual chamou-se de Fusion. A linguagem Fusion permite a modelagem das aplicações baseadas na orientação a objetos através de abstrações capazes de realizar a ligação aos dispositivos GPUs.

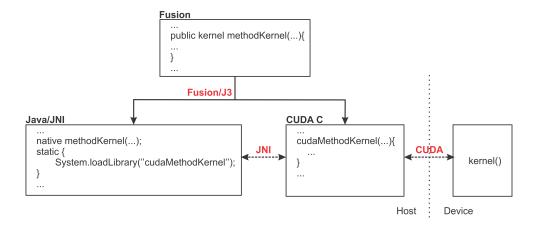

As abstrações propostas para linguagem estão intimamente relacionadas a um tipo específico de objeto, chamado de *objeto acelerador*, responsável por realizar a "ponte" entre o processador hospedeiro (*multicore*) e dispositivo GPU (*manycore*). Um objeto acelerador tem por premissa expressar o poder computacional dos dispositivos GPU e ao mesmo tempo esconder sua complexidade, mantendo encapsulado no objeto todo o paralelismo de partes críticas da aplicação. Nesse contexto, a linguagem Fusion propõe o conceito original de paralelismo entre *kernels*, na forma de *kernels* paralelos sob a abstração de *unidades* de objetos aceleradores.

Assim, cada thread é responsável pela instanciação de uma unidade do objeto acelerador, que por sua vez abre um canal de comunicação específico entre processador hospedeiro e dispositivo GPU, pelo qual os métodos do objeto poderão ser lançados para execução sobre a arquitetura GPU. Essa é a principal contribuição da linguagem Fusion, ou seja, permitir que uma aplicação Java multithread executando sobre um processador hospedeiro multicore possa se comunicar com um dispositivo GPU.

A conexão entre processador hospedeiro e dispositivo GPU é projetada de forma a ser mantida transparente para a aplicação, ou seja, a linguagem Fusion permite que objetos comuns dessa aplicação possam ser substituídos por objetos aceleradores sem muitas mudanças no código, e vice-versa, sem comprometer a estrutura da aplicação. Logicamente que essa substituição só pode acontecer entre objetos equivalentes, que possuam a mesma interface de comunicação e realizem a mesma função.

Finalmente, são desenvolvidos estudos de caso para validação do modelo proposto. Duas aplicações modeladas nas linguagens envolvidas nesse projeto (Java, CUDA C e Fusion) são usadas para demonstrar a utilização das abstrações e a estruturação das aplicações sobre a linguagem Fusion.

#### 1.7 Organização do Documento

Seguido desse capítulo introdutório, essa dissertação possui outros cinco capítulos, descritos a seguir.

O Capítulo 2 apresenta o contexto em que está inserido a área da pesquisa desse trabalho, relatando a evolução e o desenvolvimento dos aceleradores GPUs.

Além disso, será apresentada brevemente a arquitetura CUDA e detalhes sobre a arquitetura Kepler GK110, de especial interesse nesse trabalho.

O Capítulo 3 aborda os principais trabalhos relacionados sobre projetos de interfaces e linguagens de programação para GPGPU, apresentando algumas especificidades de cada um. O capítulo tem por objetivo, além de apresentar as ferramentas atuais, identificar suas limitações e quais as soluções adotadas para abordar a computação GPGPU.

O Capítulo 4 apresenta a linguagem Fusion, com foco nas abstrações desenvolvidas para ela. Características do modelo de programação adotado também poderão ser analisadas, desde sua sintaxe até a maneira como a linguagem lida com a conexão entre processador hospedeiro e dispositivo GPU.

O Capítulo 5 apresenta uma proposta inicial para prototipação do compilador Fusion. Ainda nesse capítulo, são apresentados dois estudos de caso para validação parcial do modelo proposto, bem como uma melhor compreensão do uso de objetos aceleradores pelas aplicações.

Finalmente, o Capítulo 6 discute os objetivos alcançados nessa dissertação e as principais dificuldades encontradas durante a sua realização. Serão também apresentados alguns tópicos identificados para futuros trabalhos.

## Capítulo 2

## Computação com Unidades de Processamento Gráfico (GPU)

As unidades de processamento gráfica (GPU) surgiram no final da década de 70 com o propósito de aumentar a eficiência e o poder de processamento gráfico em duas dimensões. Os primeiros aceleradores para três dimensões surgiram em 1995. Até o início dos anos 2000, os aceleradores possuíam apenas essa finalidade [NVIDIA 2013].

A partir de meados dos anos 2000, tornou-se significativo e crescente o interesse no uso de GPUs para computação de propósito geral. Sua evolução permitiu a integração de múltiplas unidades de processamento simples, obtendo um desempenho superior ao alcançado pelas arquiteturas convencionais. Posteriormente, foram inseridas novas unidades programáveis, chamados sombreadores (do inglês, shaders), as quais possibilitaram a realização de outras funções além de cálculos gráficos. A primeira GPU programável surgiu em 2001, e passaram a ser conhecidos também como processadores gráficos [NVIDIA 2013].

Em 2006, foi introduzida a abstração de programação conhecida como sombreadores de geométria (do inglês, geometry shaders), que permite ao programador criar seus próprios métodos de processamento [Nguyen 2007] [Blythe 2006]. Isso tornou possível de fato a utilização de aceleradores gráficos para a computação de propósito geral, possibilitando o surgimento das primeiras linguagens específicas para GPGPU (General-Purpose Graphical Processing Units). Além desses fatores de natureza técnica, associa-se também o custo/benefício associado a utilização de uma placa gráfica em aplicações onde o desempenho é o ponto

2.1. Arquitetura GPU

crítico como uma das principais motivações para o interesse por esses dispositivos computacionais.

#### 2.1 Arquitetura GPU

O modelo no qual é baseada a arquitetura das placas GPU modernas é conhecido como SIMD (Single Instruction Multiple Data) ou streaming data-paralell arithmetic architecture. Sua utilização limita-se a execução de uma única linha de instruções em partes disjuntas de uma estrutura de dados distribuída entre os núcleos de processamento. Nesse modelo, cada unidade de processamento executa a mesma sequência de operações sobre um fluxo de dados independente em relação às outras unidades.

A programação sobre GPUs só foi possível a partir da quarta geração das placas gráficas, através da utilização de APIs (Application Programming Interface) especializadas, diretamente sobre a placa de vídeo. No entanto, sua utilização ainda era um desafio para os programadores devido a sua complexidade, exigindo grande conhecimento das APIs e da arquitetura alvo. Além disso, os sombreadores mostraram-se pouco apropriados para a computação de propósito geral. A principal mudança nessa geração foi no pipeline gráfico, o qual define os estágios pelos quais os dados são processados pela GPU.

Atualmente, existem linguagens específicas para programação sobre aceleradores gráficos. Por exemplo, a linguagem CUDA C é a mais conhecida, de propriedade da empresa NVIDIA. Essas linguagens permitem a programação de alguns componentes dos dispositivos aceleradores, expondo a GPU como um processador aritmético. Nos primórdios, componentes executavam apenas operações pré-configuradas através das APIs.

Aplicações que fazem uso eficiente de placas GPU possuem grande demanda por recursos computacionais, relacionada a realização de processamentos sobre grandes estruturas de dados que podem ser facilmente realizados em paralelo sobre partições disjuntas dessas estruturas.

#### 2.1.1 Pipeline Gráfico

Um pipeline é uma técnica utilizada com o intuito de acelerar a velocidade de execução de instruções, aumentando também a quantidade de dados processados em paralelo. Os dados são paralelizados em estágios independentes, aumentando a produtividade com a execução de instruções no mesmo instante. Os estágios associados a um pipeline gráfico são:

2.1. Arquitetura GPU 14

► Geração de vértices - nesta primeira etapa, a aplicação repassa para o pipeline um conjunto de vértices que é transformado em um fluxo de dados (stream) que permite que sejam processados individualmente;

- ▶ Geração de Primitivas o conjunto de vértices é então transformado em uma forma geométrica, onde um conjunto de dois vértices formam um linha, três vértices formam um triângulo, e assim por diante;

- ► Geração de Fragmentos também conhecida com rasterização, onde determina-se quais *pixels* serão cobertos por cada primitiva, delineando um conjunto de fragmentos;

- ▶ Processamento de Fragmentos etapa com maior custo computacional, pois compreende a coloração dos fragmentos juntamente com as informações cromáticas e sobre os materiais de superfície utilizados;

- ► Composição etapa final, onde a imagem final é construída.

As APIs originais, OpenGL (*Open Graphics Library*) e DirectX3D, são conhecidas por apresentarem um *pipeline* fixo, no qual seu funcionamento é pré-definido, omitindo do programador a sua implementação.

#### 2.1.2 Pipeline Programável

Com o aumento na busca por efeitos gráficos mais complexos, foram necessárias mudanças que tornaram possível ao desenvolvedor da implementação modificar o comportamento de algumas etapas do *pipeline*, uma vez que APIs tradicionais como as citadas anteriormente não davam suporte a efeitos muito complexos, limitando o programador.

Em busca de flexibilizar o desenvolvimento em algumas etapas, permitiu-se que seu comportamento fosse alterado através de programas executados na GPU, conhecidos como sombreadores (do inglês, shaders). O conjunto de instruções desses programas permite definir operações a serem executadas sobre as etapas do pipeline gráfico. Os três tipos de sombreadores são:

- ► Sombreador de Vértice: permite a inserção de efeitos 3D aos objetos de uma cena, através da manipulação de cor, posição e textura;

- ► Sombreador de Geometria: recebe dados do sombreador de vértice, como primitivas, e responsabiliza-se pela renderização da cena;

▶ Sombreador de Pixel: responsável por efeitos de luz e cor dos pixels.

#### 2.2 GPGPU ou GPU Computing

O modelo de programação seguido pelas unidades programáveis da GPU é baseado no SPMD (Single Program Multiple Dada). Nesse modelo, a GPU processa muitos elementos em paralelo utilizando o mesmo programa. Para isso, os elementos necessariamente devem ser independentes, entre os quais não há comunicação. Ou seja, um programa implementado para uma GPU deve possuir muitos elementos paralelos e um único algoritmo para processá-los. Esse modelo é mais adequado para códigos ditos de linha reta, com muitos elementos sendo processados em etapas exatamente sobre o mesmo código, apropriado para arquiteturas SIMD.

Em programação de propósito geral, um programa utiliza a GPU da mesma maneira que um programa gráfico. Porém, seu mapeamento para a GPU pode ser complexo. Apesar de as operações aritméticas serem as mesmas, e podem facilmente ser seguidas, a terminologia é diferente. Pharr e Fernando 2005 demonstra como esse mapeamento pode ser realizado, mostrando como a terminologia adotada em computação gráfica pode ser adaptada para a computação de propósito geral.

Para a implementação de um programa com ênfase na computação gráfica, um desenvolvedor deve concentrar-se nos seguintes aspectos, relacionados ao *pipeline* gráfico descrito anteriormente:

- i. O programador define uma figura geométrica, que será fragmentada na etapa de geração de fragmentos, cobrindo cada pixel;

- ii. Cada fragmento será tratado pelo sombreador definido pelo programador;

- iii. O código calcula o valor do fragmento através de operações matemáticas, enquanto a memória global obtém dados a partir de uma memória de texturas;

- iv. A imagem resultante poderá então ser utilizada como textura em novas passagens pelo *pipeline*.

Nos primórdios, a utilização da GPU deveria seguir as etapas do *pipeline* gráfico para a finalidade de computação de propósito geral. Como mostrado, seguimos o exemplo citado por Owens et al. 2008, onde é realizada uma simulação de fluidos:

i. O programador especifica uma primitiva geométrica que cobrirá um domínio de interesse. Na etapa de geração de fragmentos, será gerado um fragmento para cada pixel coberto por essa primitiva;

- ii. Na etapa seguinte, um sombreador específico cobrirá cada fragmento, ou seja, cada ponto executará o mesmo programa (SPMD);

- iii. Assim como na computação gráfica, o valor atual de cada ponto será calculado através de um conjunto de operações matemáticas, aplicando-se uma operação gather para reunir os valores atuais dos pontos vizinhos que são necessários no cálculo;

- iv. O resultado será armazenado na memória global e poderá ser utilizado como entrada para outra passagem no pipeline.

A principal dificuldade encontrava-se na necessidade de utilizar APIs gráficas para a implementação de propósito geral. Com isso, o desenvolvimento do programa deve seguir exatamente as etapas do *pipeline* gráfico, o que não é bem visto pelos programadores que preferem trabalhar diretamente sobre as unidade programáveis. As APIs buscaram minimizar essa dificuldade permitindo o acesso direto às unidades, deixando o desenvolvimento mais natural sem a necessidade de interfaces gráficas, estruturando o desenvolvimento da seguinte maneira:

- i. O programador define diretamente seu domínio de interesse e estrutura sua grade de threads;

- ii. Um sombreador calcula o valor para cada thread, implicitamente sem que o programador se preocupe com essa operação;

- iii. O programa realiza cálculos computacionais, utilizando uma operação gather para ler os valores da memória global e uma operação scatter para escrever. Nesse caso, o mesmo buffer pode ser utilizado tanto para leitura quanto escrita, favorecendo algoritmos mais flexíveis com menor uso de memória;

- iv. O resultado final poderá ser utilizado para novas computações.

Esse modelo permite ao programador especificar o paralelismo de dados diretamente no programa, além de, devido ao acesso direto às unidades programáveis, poder utilizar uma linguagem mais familiar, facilitando a implementação e depuração de seus programas.

2.3. Evolução 17

#### 2.3 Evolução

Os principais desafios no desenvolvimento de CPUs encontram-se no consumo de energia e acesso a memória. Atualmente, o desenvolvimento está centrado na adição de novos núcleos, porém ainda limitando-se a uma quantidade que varia entre 4 e 8 núcleos, representando a classe dos processadores de múltiplos núcleos (do inglês, multi-core processors). Novas arquiteturas surgem a cada dia e novas promessas e expectativas são geradas, como a ideia da fusão de GPU e CPU em um único chip. Por sua vez, GPUs possuem centenas ou milhares de núcleos, especializados no processamento paralelo e massivo, sendo enquadradas na classe dos processadores de muitos núcleos (do inglês, many-core processors).

Resumindo as principais características de cada arquitetura, claramente existem diferenças fundamentais oriundas das suas premissas de projeto distintas. Por exemplo, o objetivo de uma CPU concentra-se na execução de uma única thread, composta por instruções sequencias, o mais rápido possível, enquanto que uma GPU busca a execução paralela de milhares de threads. Para realizar todo controle de operações e instruções de maneira eficiente, a CPU utiliza seus transistores para executar uma sequência de tarefas, enquanto a GPU é especializada em executar milhares de instruções paralelas. De fato, seus transistores estão dedicados a dar maior vazão ao processamento dos dados e não para controle de fluxo de execução.

Com relação ao emprego de memórias cache, a técnica que é fundamental para aumentar a vazão de dados entre memória principal e processador em CPUs tradicionais, a GPU possui uma unidade pequena associada a vários controladores de memória independentes, obtendo uma maior largura de banda, tornando possível a execução de milhares de threads em paralelo. Diferente das CPUs, o acesso a essas unidades é previsível e pode parte dela ser controlado pelo programador, tornando seu uso mais eficiente e de acordo com o padrão de acesso a memória particular do programa. Com isso, uma GPU é capaz de executar centenas de threads por multiprocessador, enquanto que uma CPU executa de 2 a 4 threads por núcleo.

Na Tabela 2.1, é possível comparar algumas características de CPUs e GPUs, comparando um processador Intel Xeon E7 e uma placa de vídeo NVIDIA Tesla.

2.3. Evolução 18

|                     | Intel Xeon E7        | NVIDIA Tesla K20X   |  |

|---------------------|----------------------|---------------------|--|

| Poder Computacional | 371 GFlops           | 2.06 TFlops         |  |

| #Cores              | 8                    | 2688                |  |

| Largura de Banda    | $51.2~\mathrm{GB/s}$ | $250~\mathrm{GB/s}$ |  |

| Preço               | $\geq$ \$ 3.600,00   | ≥ \$ 3.200,00       |  |

Tabela 2.1: Comparação entre Xeon E7 e Tesla K20X - Fevereiro 2013

Para analisar a evolução das GPUs, a partir da introdução da tecnologia 3D (era pré-GPU), tomamos como base as placas desenvolvidas pela empresa NVIDIA. Na Tabela 2.2, podemos notar o avanço tecnológico. O número de núcleos de GPUs dobra a cada 18 meses, assim como o número de transistores.

| Data | Dispositivo       | Transistores Núcleos                         |      | Tecnologia                      |  |

|------|-------------------|----------------------------------------------|------|---------------------------------|--|

| 1997 | RIVA 128          | $3  { m milh\~o}{ m es}$                     | -    | acelerador 3D                   |  |

| 1999 | ${ m GeForce256}$ | $25~\mathrm{milh\~oes}$                      | -    | primeira GPU                    |  |

| 2001 | GeForce 3         | $60 \text{ milh} \tilde{\text{o}} \text{es}$ | -    | primeiro sombreador programável |  |

| 2002 | GeForce FX        | 125 milhões                                  | -    | precisão dupla                  |  |

| 2004 | GeForce 6800      | 222 milhões                                  | 1    | GPGPU                           |  |

| 2006 | GeForce 8800      | 681 milhões                                  | 128  | CUDA                            |  |

| 2008 | GeForce GTX 280   | 1.4 bilhões                                  | 240  | CUDA e OpenCL                   |  |

| 2009 | FERMI             | 3 bilhões                                    | 512  | 64-bit end., caching            |  |

| 2011 | Kepler GK104      | $3.5~{ m bilh\~oes}$                         | 1536 | Fabricação 28 nm, SMX           |  |

| 2012 | Kepler GK110      | $7.2  \mathrm{bilh\~oes}$                    | 2880 | Dynamic Parallelism, Hyper Q    |  |

**Tabela 2.2:** Evolução das placas da NVIDIA [NVIDIA 2013]

Nesta dissertação, tomamos por base as placas da empresa NVIDIA, a qual tem notoriamente ditado a evolução tecnológica das GPUs em conjunto com alguns de seus parceiros. Consequentemente, adotamos as terminologias definidas por essa empresa. Durante a evolução, alguns conceitos sobre o hardware foram tomando forma. Os processadores de dados, chamados de processadores de fluxo (SP)<sup>1</sup> passaram a ser reunidos em multiprocessadores chamados de multiprocessadores de

<sup>&</sup>lt;sup>1</sup>do inglês, stream processor.

2.4. Programação

fluxo (SM)<sup>2</sup>. Os SMs possuem dezenas de SPs que podem ser acessados diretamente através de linguagens de programação específicas, tais como CUDA, nas versões iniciais para GPGPU, e, posteriormente, OpenCL. Cada SM possui registradores específicos e unidades totalmente dedicadas para operações aritméticas.

A arquitetura Fermi [Fermi 2012] foi a primeira arquitetura para GPUs voltada às necessidades de computação de alto desempenho, representando a quarta geração de placas programáveis da NVIDIA. Trouxe várias inovações que permitiam obter um desempenho muito superior em relação às placas gráficas anteriores a sua geração. A arquitetura Fermi define um endereçamento de 64 bits e introduz um novo nível de memória cache, tornando o processo de leitura e acesso aos dados mais rápido.

A arquitetura Kepler é a mais atual arquitetura de GPUs lançada pela NVIDIA, [KeplerGK110 2012], também voltada para computação de alto desempenho, porém com uma maior preocupação com o consumo de energia. A arquitetura Kepler caracteriza-se pela construção baseada em uma tecnologia de transistores de 28 nm de tamanho, contra os 40 nm de sua predecessora Fermi, justificando seu baixo consumo de energia, já que quanto menor o tamanho dos transistores menor é dissipação de calor. Além disso, introduz uma remodelagem nos SM que passaram a ser chamados de SMX. Mais detalhes dessa nova arquitetura serão apresentados na Seção 2.6.1.

#### 2.4 Programação

Como visto na seção anterior, o desenvolvimento de aplicações de propósito geral para GPU exigia um grande conhecimento das APIs por parte do programador, ou seja, poucos desenvolvedores eram capacitados para explorar ao máximo o desempenho de uma GPU para suas aplicações. As operações necessariamente eram executadas através de funções fixas, pré-definidas pela API.

Com o objetivo de flexibilizar o desenvolvimento, novas APIs surgiram. Por exemplo, DirectX 9 permitiu um alto nível de sombreamento e a modificação de algumas de suas funções. Porém, só podia ser programada através de uma linguagem conhecida como HLSL, desenvolvida pela Microsoft. Porém, logo surgiram linguagens mais flexíveis e acessíveis, como a GLSL (*0penGL Shading Language*) para OpenGL, e a CG (*C for Graphics*) da NVIDIA, que também permitia a implementação para múltiplos alvos, tais como DirectX e OpenGL. Apesar do surgimento dessas novas linguagens, ainda eram muito restritas ao uso

<sup>&</sup>lt;sup>2</sup>do inglês, streaming multiprocessor

das APIs, tornando seu uso uma tarefa árdua, comprometendo a produtividade dos programadores, que deveriam ser especializados nesse tipo de linguagem.

Com isso, muitos pesquisadores voltaram sua atenção para o desenvolvimento de linguagens de mais alto nível, que abstraíssem a GPU como um processador de streams. Um programa que segue o modelo de streams deve expressar o paralelismo, a comunicação e a transferência de dados utilizando os recursos da GPU. Esse programa deve possuir um conjunto de instruções, um conjunto ordenado de dados e um kernel. No kernel, o programador define a grade computacional e as funções que serão aplicadas a cada elemento dos dados de entrada, através de uma ou mais threads topologicamente organizados segundo a grade computacional.

A primeira linguagem, oriunda do meio acadêmico, foi a BrookGPU [Buck et al. 2004], que abstrai os conceitos gráficos, enfatizando a representação de dados como streams e a computação como um kernel. Os kernels são escritos com um subconjunto restrito de instruções da linguagem C. Em geral, não são utilizados ponteiros. O kernel é mapeado para o dispositivo como um código de fragmento de sombreamento e os dados como texturas. Entradas e saídas são realizadas explicitamente com operações de leitura e escrita.

Grandes empresas, percebendo o interesse da comunidade científica nas GPUs, não somente como hardware gráfico, mas também como acelerador para diferentes aplicações, começaram o desenvolvimento de ferramentas para expor a GPU como um processador de propósito geral. As linguagens mais utilizadas atualmente para programação sobre GPUs são desenvolvidas pelas empresas NVIDIA e Khronos Group [Kronos 2012]. A NVIDIA lançou a linguagem conhecida como CUDA C, enquanto a antiga ATI iniciou o desenvolvimento da linguagem Brook++, baseada na linguagem BrookGPU. Atualmente, a AMD (Advanced Micro Devices), proprietária da antiga ATI, propõe uma SDK (Software Development Kit) para a linguagem OpenCL (Open Computing Language), desenvolvida pelo grupo Khronos.

#### 2.5 CUDA

Como visto anteriormente, a arquitetura CUDA tem como principal objetivo encapsular as APIs gráficas e expor a GPU como um processador aritmético, Criado em 2007 pela NVIDIA, é uma extensão da linguagem C, permitindo o desenvolvimento de programas que executam, em parte, nas GPUs. Esses trechos de código são conhecidos como kernels.

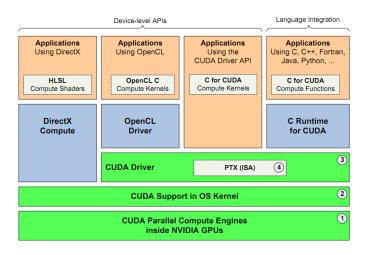

Figura 2.1: Arquitetura Cuda [CUDA1.1 2012]

#### 2.5.1 Arquitetura

A partir da geração G80 das placas GPU NVIDIA [NVIDIA 2013], a empresa começou o desenvolvimento da arquitetura CUDA, que considera hardware e software, composta pelos seguintes componentes:

- 1. Dispositivo Físico;

- Suporte para inicialização de hardware;

- 3. Driver para desenvolvedores;

- 4. Interfaces de programação em nível de dispositivo, tais como DirectX ou OpenCL, ou mais alto nível, tais como C Runtime for CUDA.

Além disso, CUDA fornece integração com outras linguagens, tais como JAVA, Python, Fortran, dentre outros. O ambiente ainda disponibiliza exemplos, bibliotecas padrão otimizadas (BLAS e FFT), compilador (nvcc) e depurador (cudagdb). Na Figura 2.1, é possível observar a arquitetura CUDA mais detalhadamente.

#### 2.5.2 Modelo de Programação

A API CUDA visualiza o dispositivo GPU como um co-processador para a CPU hospedeira, sendo responsável pela execução paralela de blocos básicos de código computacionalmente intensivos e com funções bem caracterizadas através de threads, enquanto que a CPU responsabiliza-se pelo controle do fluxo de execução. Dessa forma, o fluxo de execução parte do hospedeiro, inicializando um conjunto de dados

(vetor) que serão copiados para memória global do dispositivo. Por sua vez, o dispositivo realiza os cálculos sobre o conjunto de dados. Ao final da execução, os dados são copiados de volta para o hospedeiro.

O código a ser executado no dispositivo deve ser escrito em um trecho de código específico chamado kernel. O kernel não pode conter chamadas a outras funções fora do seu escopo, e não permite recursão. Um kernel é denotado em uma função especifica identificada pelo marcador <u>global</u>:

```

__global__ myKernel (arguments){

....

}

```

A chamada para esse trecho de código pode ocorrer em qualquer parte do código fonte seguindo a seguinte notação:

```

myKernel <<dimGrid, dimBlock>> (arguments);

```

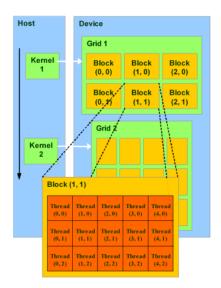

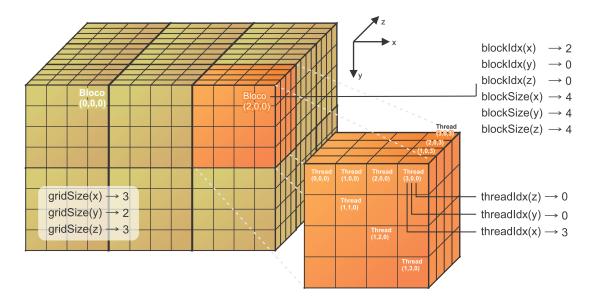

As threads são agrupadas em blocos e mapeadas para os SMs. Em geral, existem mais threads do que um multiprocessador pode executar em paralelo. O número de blocos também pode ser maior que o número de SMs, não sendo necessário recompilação para execução em arquiteturas com diferentes capacidades. Os blocos são organizados em grades e mapeados aos SPs.

O controle de execução pode ser realizado através da utilização de barreiras de sincronização. Como o controle do fluxo é executado sobre as threads em um bloco e não sobre os dados, o modelo de programação da arquitetura CUDA (Figura 2.2) é denominado SIMT (Single Instruction Multiple Thread) [CUDA4.1 2012]. Cada SP executa suas threads intercalando suas instruções, técnica conhecida como IMT (Interleaved Multithreading) [Munshi et al. 2005]. A escalabilidade da arquitetura ocorre principalmente pela adição de novos SMs.

A unidade responsável pelo controle de uma linha de instruções de um conjunto de threads em um bloco é conhecida como warp. Um warp pode controlar até 32 threads, sendo executadas 4 threads em pipeline. Na arquitetura Kepler, cada multiprocessador possui quatro unidades warp, diferenciando-se da arquitetura Fermi que possuía apenas duas unidades desse tipo.

#### Hierarquia de Memória

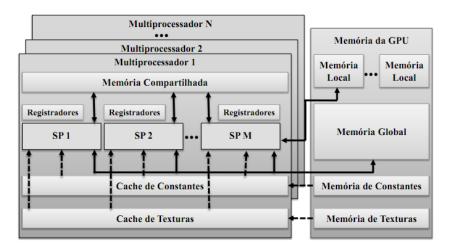

Um dispositivo possui diferentes níveis de memória (Figura 2.3), os quais seguem a hierarquia de *threads* e dos processadores. Cada SP possui sua própria memória

Figura 2.2: Modelo de programação [CUDA4.2 2012]

individual, representada por registradores de 32 bits extremamente rápidos, que podem ser utilizados de maneira concorrente pelas threads que executam sobre o SP. Seguindo a hierarquia, cada bloco de threads em um SM possui acesso à memória compartilhada que é acessada por todas as threads que o compõem. As caches são memórias somente para leitura, compartilhadas entre os SPs em um mesmo SM. O principal objetivo dessas memórias é reduzir o número de acesso às memórias externas ao SM, possuindo tempo de acesso baixo mas com tamanho limitado.

Figura 2.3: Arquitetura da memória GPU

As memórias global, local, de constantes e de texturas são externas ao SM, sendo maiores e com uma latência mais alta. A memória global é compartilhada por todas as *threads* em todos SMs, enquanto que a memória local é individual de cada *thread*,

ambas para leitura e escrita. As memórias de constantes e texturas são memórias otimizadas e acessíveis por todas as *threads*. As caches contidas internamente aos SMs são de acesso a essas memórias. Na Tabela 2.3, é apresentado um resumo das características dos espaços de memória em diferentes níveis de hierarquia.

| Memória             | Localização<br>- SM | Tamanho              | Latência<br>(ciclos) | Escopo | Acesso              |

|---------------------|---------------------|----------------------|----------------------|--------|---------------------|

| Registradores       | interna             | até 64 KB por<br>SM  | ≈ 0                  | thread | leitura/<br>escrita |

| Compartilhada       | interna             | 16 KB por SM         | $\geq 4$             | bloco  | leitura/<br>escrita |

| Cache de texturas   | interna             | depende da<br>global | 0-600                | bloco  | leitura             |

| Cache de constantes | interna             | 64 KB                | 0-600                | bloco  | leitura             |

| Global              | externa             | até 1024 MB          | 400-600              | grade  | leitura/<br>escrita |

| Local               | externa             | depende da<br>global | 400-600              | thread | leitura/<br>escrita |

| Texturas            | externa             | 1.4 bilhões          |                      | grade  | leitura             |

| Constantes          | externa             | 3 bilhões            |                      | grade  | leitura             |

Tabela 2.3: Resumo características da memória GPU

#### Programação

A linguagem CUDA C estende a linguagem C através de primitivas com o objetivo de permitir o acesso aos recursos da GPU escondendo a sua complexidade.

Os qualificadores de função são primitivas para identificar o local de execução de uma determinada função. São eles:

- ightharpoonup \_\_global\_\_: define um kernel;

- ▶ \_\_device\_\_: função chamada somente no dispositivo e executada somente sobre o dispositivo;

- ▶ \_\_host\_\_: define uma função chamada somente no hospedeiro e executada somente sobre o hospedeiro;

Os qualificadores de variáveis são utilizados para sinalizar em qual nível da hierarquia de memória determinada variável será alocada:

▶ \_\_device\_\_: define uma variável a ser alocada na memória global do dispositivo GPU, tornando-se acessível por todas as threads;

- ▶ \_\_constant\_\_: especifica uma variável alocada na memória de constantes;

- ▶ <u>\_\_shared\_\_</u>: define uma variável alocada no espaço compartilhado, sendo acessível apenas pelas *threads* do mesmo bloco.

As primitivas **\_\_global**\_\_ e **\_\_device**\_\_ introduzem algumas restrições às funções:

- i. não suportam recursão;

- ii. não podem conter variáveis declaradas como estáticas; e

- iii. não podem conter um número variável de argumentos.

Não é possível recuperar o endereço de uma função declarada com o modificador \_\_device\_\_. Por sua vez, funções declaradas com o modificador \_\_global\_\_ são assíncronas e devem especificar a dimensão da grade e dos blocos. As dimensões são especificadas através de variáveis do tipo dim3, que definem vetores de inteiros. Os mecanismos utilizados para manipulação e definição da grade são:

- ► gridDim: contêm a dimensão da grade;

- ▶ blockIdx: contêm o índice do bloco dentro da grade;

- ▶ blockDim: contêm a dimensão do bloco;

- ► threadIdx: contêm o índice da thread dentro do bloco;

- ▶ warpSize: contêm o número de threads no warp.

Toda escrita em uma variável do tipo <u>\_\_shared\_\_</u> só poderá ser vista por todas as *threads* após a passagem pela barreira de sincronização, realizada através da primitiva <u>\_\_syncthreads()</u>.

No Código 2.1, é possível observar a utilização das primitivas, e como é realizada a transferência de dados entre a CPU hospedeira e o dispositivo GPU. No Código 2.2, um exemplo de definição do *kernel* para ser executado na GPU é apresentado.

Código 2.1: Multiplicação de Matrizes em CUDA: Hospedeiro

```

int main (int argc, char *argv[]){

int *A, *B, *C,

*A_d, *B_d, *C_d;

cudaMalloc ((void **)&A_d, total_bytes);

cudaMalloc ((void **)&B_d, total_bytes);

cudaMalloc ((void **)&C_d, total_bytes);

cudaMemcpy(A_d, A, total_bytes, cudaMemcpyHostToDevice);

10

11

cudaMemcpy(B_d, B, total_bytes, cudaMemcpyHostToDevice);

12

dim3 gride (LARGURA/SUB_LARGURA, LARGURA/SUB_LARGURA);

14

dim3 bloco (SUB_LARGURA, SUB_LARGURA);

15

matMulGPU <<<gride, bloco>>> (A_d, B_d, C_d);

16

17

cudaMemcpy(C, C_d, total_bytes, cudaMemcpyDeviceToHost);

18

19

cudaFree(A_d);

20

21

cudaFree(B_d);

cudaFree(C_d);

22

23

24

return 0;

25 }

```

Nas linhas 3 e 4, do código 2.1, são definidos os dados da aplicação. Na linha 3, são definidas as matrizes armazenadas na memória do hospedeiro. Na linha 4, essas matrizes são armazenadas na memória do dispositivo. Toda variável a ser utilizada no dispositivo deve ser reservada na memória global antes de iniciar sua computação. Essa operação ocorre no bloco de código nas linhas 6-8, através do comando cudaMalloc((void\*\*) &A\_d, total\_bytes), onde &A\_d corresponde ao endereço inicial na memória que vai possuir o tamanho passado como argumento em total\_bytes.

Os dados são copiados para a memória do dispositivo nas linhas 10 e 11, através do comando cudaMemcpy( $A\_d$ , A,  $total\_bytes$ , cudaMemcpyHostToDevice). Esse comando possui quatro argumentos na seguinte ordem: (i) variável de destino, (ii) variável de origem, (iii) quantidade de dados e (iv) tipo de operação de transferência. As operações possíveis para transferência são:

- ► cudaMemcpyHostToDevice: cópia do hospedeiro para o dispositivo;

- ► cudaMemcpyDeviceToHost: cópia do dispositivo para o hospedeiro e;

- ► cudaMemcpyDeviceToDevice: cópia no próprio dispositivo.

2.5. CUDA 27

É necessário definir a grade computacional que será utilizada sobre o dispositivo, indicando a configuração dos blocos e o número de *threads* em cada bloco. Essas configurações são definidas, como visto, em variáveis internas. Nesse exemplo, são atribuídas nas linhas 13 e 14, para a grade e para os blocos respectivamente.

A chamada do kernel ocorre na linha 16, onde observa-se que nesse momento o programador informa a grade computacional que será utilizada por esse kernel especificamente através da sintaxe de configuração <<< grade, bloco>>>.

Os dados são copiados de volta para o hospedeiro ao final da execução do kernel na linha 18 e a memória do dispositivo é reciclada nas linhas 20-22.

Código 2.2: Multiplicação de Matrizes em CUDA: Dispositivo

```

_global__ void matMulGPU (int *A, int *B, int *C) {

__shared__ int Mds [SUB_LARGURA][SUB_LARGURA];

__shared__ int Nds [SUB_LARGURA][SUB_LARGURA];

int bx = blockIdx.x;

int by = blockIdx.y;

int tx = threadIdx.x;

int ty = threadIdx.y;

int Row = by * SUB_LARGURA + ty;

int Col = bx * SUB_LARGURA + tx;

11

12

float Pvalue = 0;

13

for (int m = 0; m < LARGURA/SUB_LARGURA; ++m){</pre>

14

15

Mds[ty][tx] = A[Row*LARGURA + (m*SUB_LARGURA + tx)];

Nds[ty][tx] = B[Col + (m*SUB_LARGURA + ty)*LARGURA];

16

17

__synchthreads();

18

19

for (int k = 0; k < SUB_LARGURA; ++k)</pre>

20

Pvalue += Mds[ty][k] * Nds[k][tx];

21

22

23

__synchthreads();

24

}

C[Row*LARGURA + Col] = Pvalue;

^{25}

26 }

```

O kernel matMulGPU é definido como uma função global na linha 1 do Código 2.2. Nas linhas 2 e 3, são definidas variáveis armazenadas na memória compartilhada do dispositivo que serão utilizadas no cálculo da multiplicação de matrizes. Os índices para localização das threads são alcançados no bloco de código das linhas 5-8. Logo, são definidas a linha e a coluna específicas da matriz para cada thread, nas linhas 10 e 11.

O paralelismo é definido através de dois laços aninhados nas linhas 14 à 24.

No primeiro laço, um bloco de dados é atualizado na memória compartilhada a cada iteração, facilitando o acesso pelo conjunto de *threads*. Essa operação deve ser sincronizada entre todas as *threads* do bloco, o que ocorre na linha 18 através do comando \_\_synchthreads().

O laço mais interno, nas linhas 20 e 21, tem por função realizar o cálculo de cada posição da matriz resultante, onde cada thread é responsável por uma linha/coluna. Antes que os dados sejam atualizados novamente, é necessário que todas as threads estejam sincronizadas, o que é realizado na linha 23.

Ao final da execução, cada thread transfere o valor calculado na variável Pvalue para posição que ficou responsável da matriz resultante C.

### 2.6 Portabilidade

Tratando-se de aplicações de computação de alto desempenho, um dos principais pontos a serem analisados é a portabilidade, que é a capacidade que um código escrito deve possuir de obter desempenho aceitável em dispositivos diferentes, ou seja, que não seja necessário reescrever o código toda vez que o usuário tenha necessidade de utilizar um dispositivo diferente.

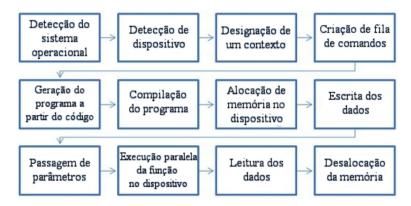

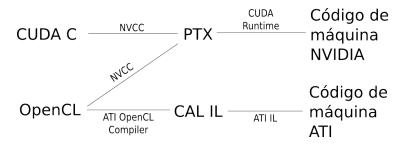

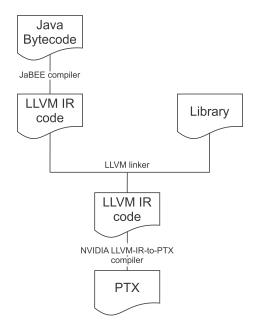

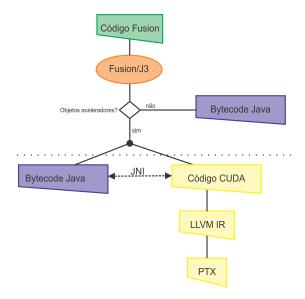

A portabilidade da arquitetura CUDA se dá somente entre dispositivos NVIDIA e, dependendo das primitivas utilizadas, com o mesmo compute capability. Essa portabilidade é garantida através do seu compilador NVCC (NVIDIA Compiler Collection), baseado no LLVM (Low-Level Virtual Machine) [Illinois 2012], como ilustrado na Figura 2.4. O compilador invoca diversas ferramentas para diferentes estágios de compilação. Determina-se qual modelo deverá ser utilizado de acordo com as informações coletadas sobre o modelo da GPU alvo no momento da inicialização da aplicação.

Inicialmente, o compilador realiza o tratamento dos marcadores introduzidos pela linguagem CUDA C/C++, a fim de separar os códigos específicos de cada arquitetura, C puro, para o host, e cubin, para o dispositivo. Um preprocessador do grupo EDG (Edson Design Group) separa esse códigos em arquivos diferentes. O código C é então compilado por um compilador nativo enquanto o código cubin é compilado pelo LLVM. O compilador LLVM consiste de um front-end e um back-end. O front-end traduz o código-fonte para código LLVM IR (LLVM bytecode). Por sua vez, o back-end traduz esse bytecode em código assembly, chamado de PTX (Parallel Thread eXecution). Em uma segunda etapa, ocorre a geração de um código específico para o modelo da GPU a partir do código PTX. Na Figura 2.5 é possível analisar

Figura 2.4: Compilador CUDA [CUDA 2013]

o código PTX gerado a partir de um código CUDA, exemplo retirado de Nickolls e Kirk [Patterson e Hennessy 2008] que calcula um produto vetorial.

```

.entry saxpy ( .param .s32 n, .param .f32 alpha,

.param .u64 x , .param .u64 y ) {

.reg .u16 %rh <4 >; .reg .u32 %r <6 >; .reg .u64 %rd <8 >;

.reg .f32 %f <6 >; .reg .pred %p<3 >;

_Z9saxpy_GPUifPfS_

$LBB1_

mov .u16

%rh1, %ctaid.x;

%rh2 , %ntid.x;

mov.u16

%r1, %rh1, %rh2;

mul .wide .u16

cvt .u32 .u16

%r2, %tid.x;

add .u32

%r3, %r2, %r1;

%r4, [n];

ld .param .s32

setp .le .s32

%p1, %r4, %r3;

@%p1 bra $Lt_0_770;

%rd1, %r3;

cvt .u64 .s32

mul .lo .u64

%rd2, %rd1, 4;

ld .param .u64

%rd3, [y];

add .u64

%rd4, %rd3, %rd2;

%f1, [%rd4 + 0];

ld .global .f32

%rd5, [x];

%rd6, %rd5, %rd2;

ld .param .u64

global void saxpy parallel (int n, float alpha,

add .u64

floatx, floaty) {

%f2, [%rd6 + 0];

ld .global .f32

int i = blockldx.x * blockDim.x + threadldx.x;

ld .param .f32

%f3, [alpha];

if (i < n) y[i] = alpha x[i] + y[i];

%f4, %f2, %f3, %f1;

mad .f32

st .global .f32

[\%rd4 + 0], \%f4;

$Lt 0 770:

int nblocks = (n + 255) / 256;

exit;

saxpy_parallel <<<nblocks , 256>>>(n, 2.0, x, y);

(a) Código CUDA

(b) Código PTX

```

Figura 2.5: Exemplo de código PTX gerado pelo compilador CUDA.

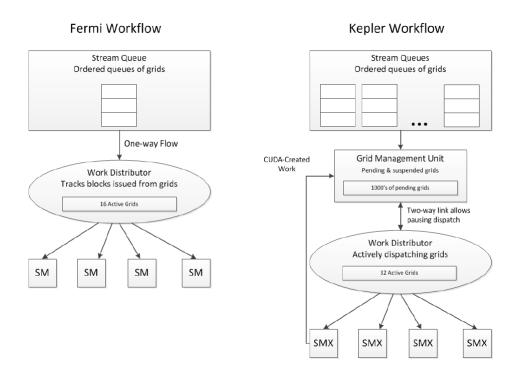

Uma alternativa para garantir portabilidade entre dispositivos em geral, válida tanto para dispositivos NVIDIA quanto para dispositivos AMD, seria a utilização da linguagem OpenCL, que também utiliza o compilador LLVM. Isso explica as